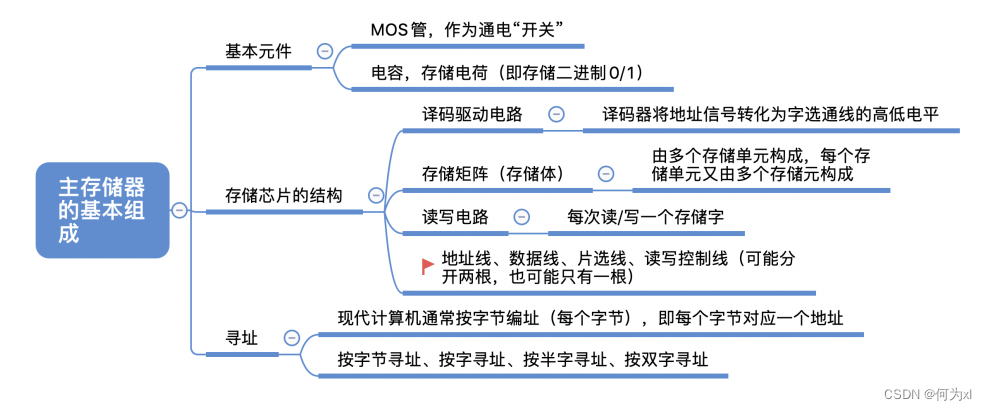

一、主存儲器的基本組成

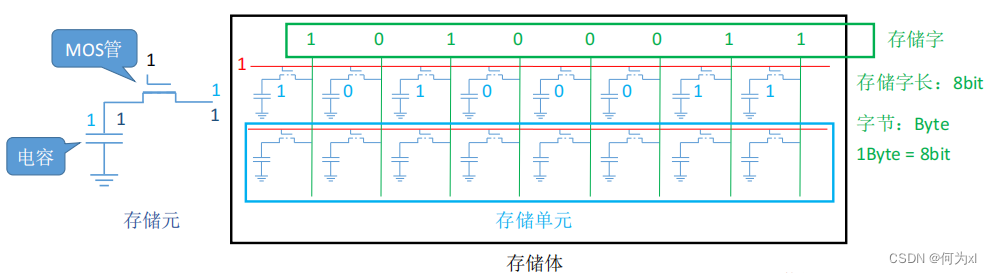

(一)、基本的半導體元件

註🤷🏽♀️:MOS管可理解為一種電控開關🦝,輸入電壓達到某個閾值時👬🏻,MOS管就可以接通🟡🧏♂️。

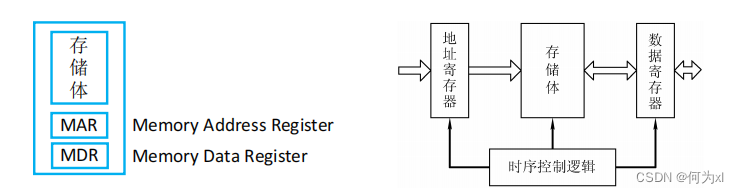

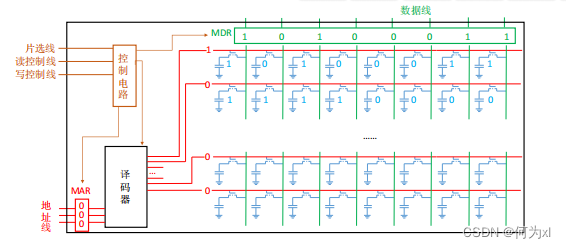

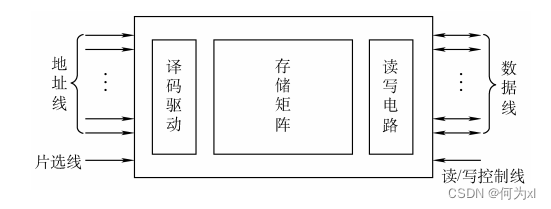

(二)👌🏻、存儲器芯片的基本原理

(三)📦、總結

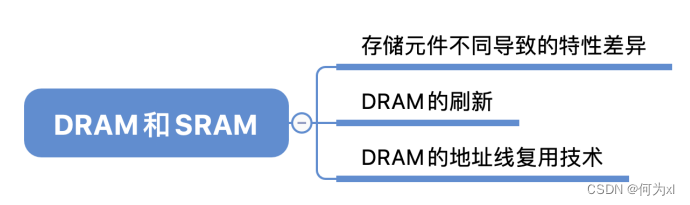

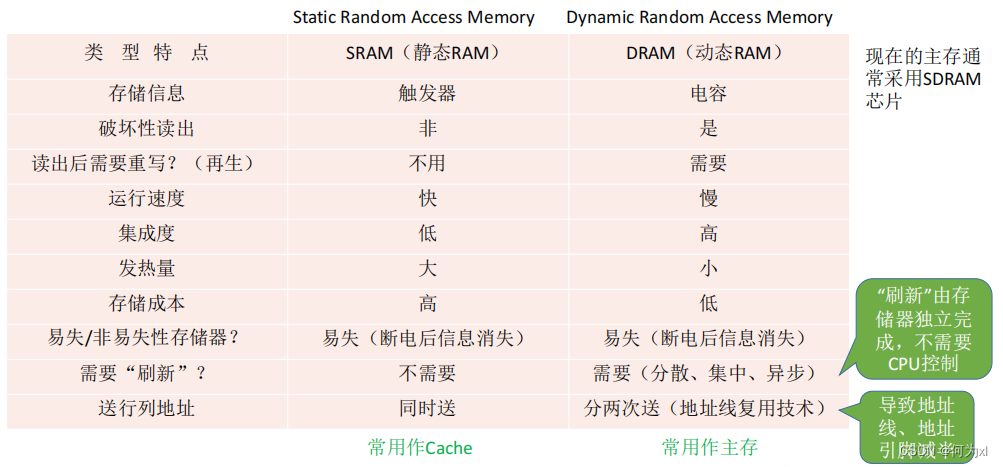

二☝️、SRAM 和 DRAM

1 動態RAM(Dynamic Random Access Memory)DRAM

2 靜態RAM(Static Random Access Memory)SRAM

DRAM用於主存、SRAM用於Cache

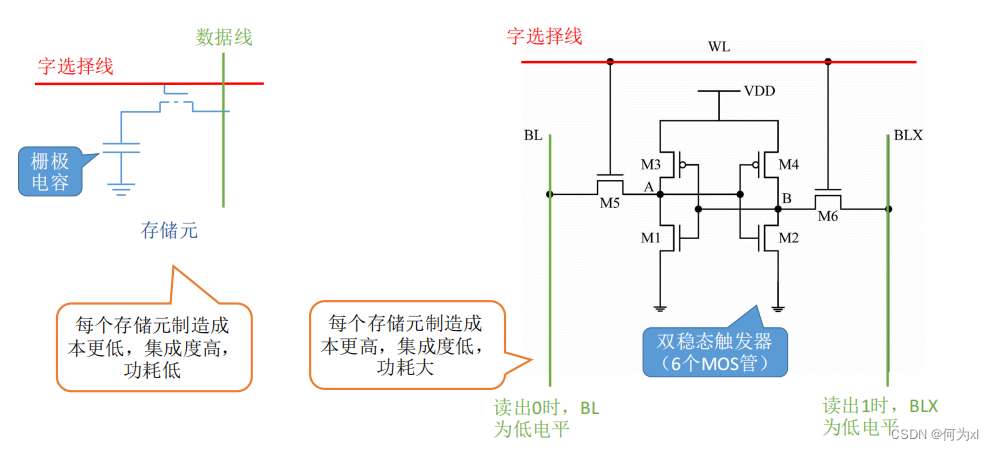

(一)、柵極電容 V.S. 雙穩態觸發器

DRAM芯片:使用柵極電容存儲信息

SRAM芯片😕:使用雙穩態觸發器存儲信息

核心區別:存儲元不一樣

可以看到雙穩態觸發器使用 6個MOS管,柵極電容使用一個 MOS 管👎,故 SRAM 與 DRAM 的一些特性可以由此得到。

柵極電容:電容內的電荷只能維持2ms。即便不斷電🐷,2ms後信息也會消失🧑🏻🦯➡️。2ms之內必須“刷新”一次(給電容充電)。

雙穩態觸發器🤴🏽:只要不斷電🔂,觸發器的狀態就不會改變。

(二)🐻、DRAM 的刷新

多久需要刷新一次? 刷新周期:一般為2ms。

每次刷新多少存儲單元?以行為單位🎅🏼,每次刷新一行存儲單元。

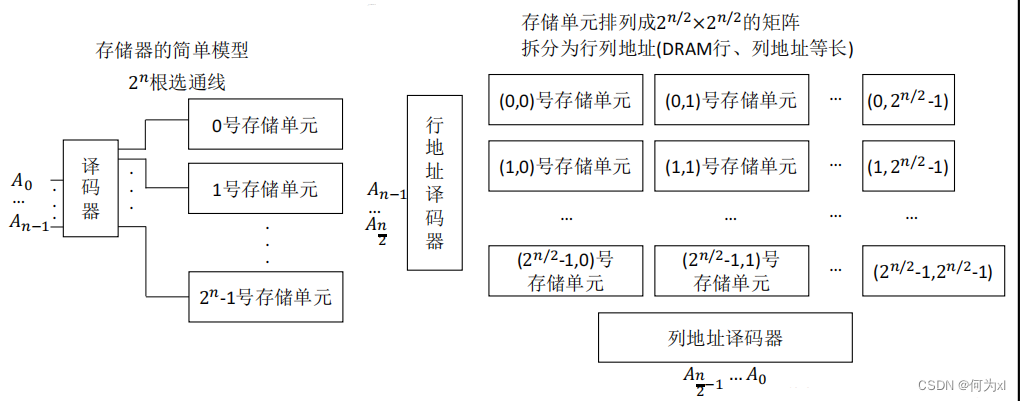

註💓:DRAM 使用行列地址🏋🏿♂️🍱,可以減少選通線的數量。

假設DRAM內部結構排列成128×128 的形式,讀/寫周期0.5us ,2ms 共 2ms/0.5us = 4000 個周期

1. 分散刷新

思路一:每次讀寫完都刷新一行👃🐴。

方式:系統的存取周期變為1us,前0.5us時間用於正常讀寫

後0.5us時間用於刷新某行。

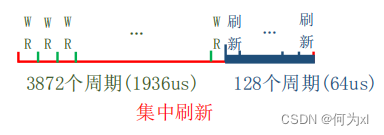

2. 集中刷新

思路二:2ms 內集中安排時間全部刷新。

方式7️⃣:系統的存取周期還是0.5us✌🏻,有一段時間專門用於刷新🍄,無法訪問存儲器🪛,稱為訪存“死區”🔊。

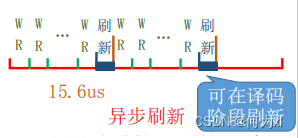

3. 異步刷新

思路三:2ms內每行刷新1次即可 。

方式🫃🏿:2ms內需要產生128次刷新請求每隔 2ms/128 = 15.6us 一次,每15.6us內有0.5us的“死時間”。

(三)🫷、DRAM 的行列地址劃分

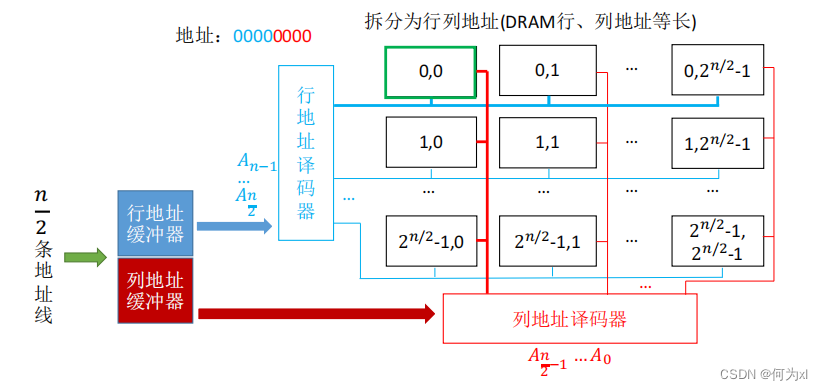

(四)、DRAM 的地址線復用技術

行、列地址分兩次送,可使地址線更少🪦,芯片引腳更少👦🏽🤙。

(五)、DRAM 與 SRAM 比較

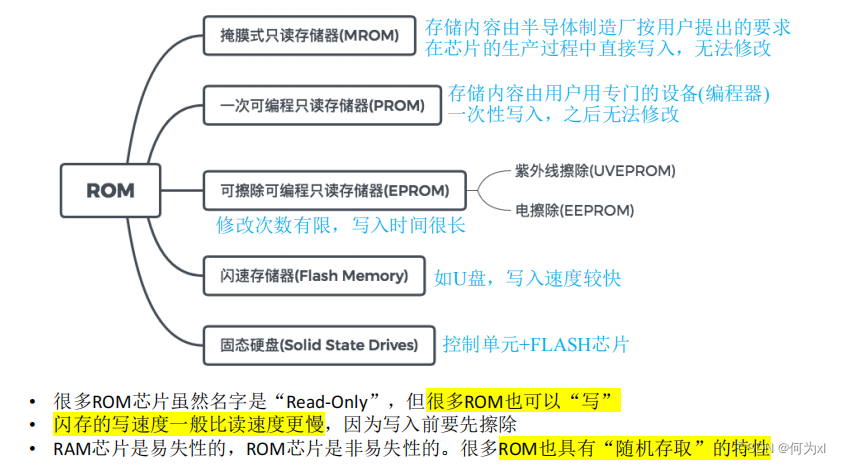

三▶️、只讀存儲器(ROM)

邏輯上👨🏻💻,主存由 RAM+ROM 組成,且二者常統一編址

RAM芯片 —— 易失性,斷電後數據消失🦸♂️。

ROM芯片 —— 非易失性👩🏿🎤,斷電後數據不會丟失。很多ROM也具有“隨機存取”的特性。

(一)🕋、ROM 的種類

任何人不可重寫(只能讀出)

寫一次之後就不可更改

可進行多次重寫

可用“電擦除”的方式☝🏿,擦除特定的字🤸🏿🧑🏿🍼。

在EEPROM 基礎上發展而來,斷電後也能保存信息🫵🏼,且可進行多次快速擦除重寫。

由控製單元+存儲單元(Flash 芯片)構成🔗,與閃速存儲器的核心區別在於控製單元不一樣,但存儲介質都類似🥎,可進行多次快速擦除重寫😌。

(二)、ROM 的總結

鏈接🔱:https://blog.csdn.net/weixin_43848614/article/details/126820846

作者:何為xl